Электроника СВЧ

УДК 621.3.049.77 Обзорная статья

https://doi.org/10.32603/1993-8985-2023-26-4-33-55

# Конструктивные подходы к интеграции приборов на основе разных полупроводниковых технологий в микроэлектронике СВЧ

А. С. Ефимов В

АО «НПП "Исток" им. Шокина», Фрязино, Россия

<sup>™</sup> easmov@gmail.com

#### Аннотация

**Введение.** Достижение высоких характеристик радиоэлектронной системы требует применения комбинации приборов, реализованных на разных полупроводниковых технологиях, – гетерогенной интеграции. Достоинства гетерогенной интеграции очевидны при компактном соединении элементов в единую схему. Развитие подходов интеграции, обеспечивающих повышенную функциональность и улучшенные рабочие характеристики, является актуальной проблемой современной электронной компонентной базы СВЧ.

**Цель работы.** Аналитический обзор современных и перспективных направлений конструктивных решений интеграции микроэлектроники СВЧ на основе разных широкозонных полупроводниковых технологий.

*Материалы и методы.* Рассмотрены 8 подходов интеграции, обеспечивающих соединение приборов на разных полупроводниковых технологиях в СВЧ-диапазоне: монолитная гетерогенная интеграция, монтаж пластина-к-пластине, метод переноса слоев, интеграция в единую подложку, интеграция методом печати, интеграция проволоками, перевернутый монтаж, hot-via. Рассмотрены конструктивные подходы интеграции, этапы реализации, достоинства и недостатки.

**Результаты.** Монолитная гетерогенная интеграция и монтаж пластина-к-пластине, как и метод переноса слоев, несмотря на минимальные длины межсоединений, имеют ряд фундаментальных ограничений, связанных с совместимостью разных полупроводниковых материалов, а также требуют больших технологических возможностей, что сдерживает их развитие и применение. Интеграция в единую подложку из-за вариативности реализации позволяет обеспечить уникальные характеристики, например благодаря интеграции магнитных материалов, однако требует высокой сложности технологических процессов интеграции. Метод перевернутого монтажа обеспечивает минимальные потери и паразитные составляющие переходных межсоединений в СВЧ-диапазоне благодаря миниатюризации переходных межсоединений. Ноt-via, как модификация метода перевернутого монтажа, обеспечивает лучшую совместимость с микрополосковыми схемами. Их дальнейшее совершенствование и массовое применение во многом зависят от развития технологии формирования локальных переходных межсоединений.

Заключение. Развитие подходов близкой интеграции в микроэлектронике СВЧ идет как в монолитном направлении — монолитная гетерогенная интеграция и монтаж пластина-к-пластине, так и в гибридномонолитном — метод переноса слоев, интеграция в единую подложку, применение аддитивных технологий, перевернутый монтаж и hot-via. Проведенный сравнительный анализ представленных методов имеет практическое применение.

**Ключевые слова:** СВЧ, гибридно-монолитная интегральная схема, широкозонные полупроводники, гетерогенная интеграция

**Для цитирования**: Ефимов А. С. Конструктивные подходы к интеграции приборов на основе разных полупроводниковых технологий в микроэлектронике СВЧ // Изв. вузов России. Радиоэлектроника. 2023. Т. 26, № 4. С. 33–55. doi: 10.32603/1993-8985-2023-26-4-33-55

Конфликт интересов. Автор заявляет об отсутствии конфликта интересов.

Статья поступила в редакцию 09.06.2023; принята к публикации после рецензирования 10.07.2023; опубликована онлайн 28.09.2023

SHF Electronics

Review article

# Approaches to Heterogeneous Integration for Millimeter-Wave Applications

Alexander S. Efimov <sup>⊠</sup>

JSC RPC "Istok" n. a. Shokin", Fryazino, Russia

<sup>™</sup>easmov@gmail.com

#### **Abstract**

*Introduction.* Enhanced performance of electronic systems can be achieved by heterogeneous integration of different semiconductor technologies. The benefits of heterogeneous integration become obvious when close connections between the devices are provided. The development of integration approaches, enabling functionality and improved performance, appears a relevant task for modern microwave microelectronics.

Aim. Review of state-of-the-art and promising heterogeneous integration concepts and techniques in microwave microelectronics.

Materials and methods. Eight integration approaches that ensure the connection of devices based on different semiconductor technologies for microwave frequencies are considered: monolithic heterogeneous integration, wafer bonding, micro-transfer printing, embedded chip assembly, print additive manufacturing, wire bonding, flip-chip, and hotvia. The integration approaches are analyzed in terms of their implementation specifics, advantages and disadvantages.

Results. Monolithic heterogeneous integration and wafer bonding, as well as micro-transfer printing, despite the

minimum interconnections, have a number of fundamental limitations. These limitations are related to the compatibility of various semiconductor technologies and the necessity of high technological capabilities. The technology of

embedded chip assembly enables the variability of implementation techniques, which makes it possible to provide

unique characteristics, e.g., due to the integration of magnetic materials. However, this approach is associated with a

high complexity of integration technological processes. Flip-chip integration ensures minimal interconnect losses

due to bump miniaturization. Hot-via, as a modification of flip-chip, provides for a better compatibility with microstrip type circuitry. Their further improvement and mass application largely depends on the development of technologies for the formation of low-pitch interconnections.

**Conclusion.** The development of close integration approaches in microwave microelectronics is proceeding both in the monolithic direction, i.e., monolithic heterogeneous integration wafer bonding, as well as in the quasi-monolithic direction, i.e., micro-transfer printing, embedded chip assembly, print additive manufacturing, flip-chip, and hot-via. The conducted comparative analysis of the presented methods has practical application.

**Keywords**: millimeter-wave, quasi-monolithic microwave integrated circuit, wide band gap semiconductors, heterogeneous integration

**For citation:** Efimov A. S. Approaches to Heterogeneous Integration for Millimeter-Wave Applications. Journal of the Russian Universities. Radioelectronics. 2023, vol. 26, no. 4, pp. 33–55. doi: 10.32603/1993-8985-2023-26-4-33-55

Conflict of interest. The author declares no conflicts of interest.

Submitted 09.06.2023; accepted 10.07.2023; published online 28.09.2023

Введение. Электронная компонентная база (ЭКБ) СВЧ развивается в части повышения уровней мощности, рабочих частот и полосы пропускания, степени функциональности и миниатюризации.

Электрическое соединение отдельных кристаллов в единый модуль является важным переходом от характеристик дискретных кристаллов к функциональной системе. В то время как монолитные интегральные схемы СВЧ имеют заметное продвижение вверх по частотному

диапазону, их электрический контакт друг с другом остается проблемным и ограничивающим фактором применения широкополосной ЭКБ СВЧ миллиметрового диапазона частот [1]. Снижение массогабаритных характеристик СВЧ-модулей, а также переход от однофункциональных схем к многофункциональным ведут к необходимости интеграции отдельных монолитных интегральных схем (МИС) СВЧ с минимальными межсоединениями.

Гибридно-монолитные интегральные схемы (ГМИС) СВЧ являются основой современной отечественной ЭКБ СВЧ. Концепция ГМИС СВЧ — интеграция отдельных готовых кристаллов активных элементов (транзисторов и МИС СВЧ) с кристаллами и платами пассивных элементов.

Концепция ГМИС СВЧ имеет 3 стимула к применению. Первый - стоимость. Современные МИС СВЧ изготавливаются на подложках с эпитаксиально выращенными гетероструктурами. Гетероструктуры необходимы для формирования активных элементов - транзисторов и диодов. Однако активные элементы занимают менее 10 % площади МИС СВЧ. Остальную площадь занимает пассивная часть, не требующая наличия гетероструктуры. Формирование гетероструктуры на полуизолирующей подложке повышает стоимость пластины в 3...5 раз. Таким образом, эффективное использование площади кристаллов является необходимым условием снижения себестоимости модулей. Более того, миниатюризация кристаллов ведет к увеличению процента выхода годных. Чем меньше процент выхода годных кристаллов МИС СВЧ, тем экономически актуальнее применение концепции ГМИС СВЧ. Применение уже готовых кристаллов активных элементов снижает время изготовления готовых схем в 2-3 раза по сравнению с монолитной конструкцией [2]. Второй стимул – преодоление ограничения монолитных схем по площади и функциональности. На практике, предельные габаритные размеры МИС СВЧ составляют 5 × 5 мм по технологическим ограничениям. Предел по габаритам препятствует реализации многофункциональных схем. Третий - возможность интеграции разных полупроводниковых технологий. Кремний является главным материалом современной полупроводниковой электроники, позволяющим реализовывать схемы с высокой степенью интеграции, сложности и наименьшей стоимостью. Актуальная кремниевая КМОП-технология обеспечивает исполнение приемопередающих МИС СВЧ, объединяя на одном кристалле цифровую и аналоговую части малой мощности. Повышение характеристик приемопередатчиков с точки зрения выходной мощности, рабочих частот и шумовых параметров требует использования приборов на основе широкозонных полупроводников, полевых транзисторов с высокой подвижностью электронов – HEMT (High Electron Mobility Transistor) и гетеропереходных биполярных транзисторов (ГБТ). Современные GaAs- и GaN-технологии обеспечивают беспрецедентный уровень выходной мощности в диапазоне до 100 ГГц. InPтехнология обеспечивает наилучшие частотные и шумовые характеристики. Приборы на широкозонных полупроводниках являются незаменимыми элементами для развития систем связи пятого и шестого поколений [3]. В табл. 1 представлены характеристики транзисторов, выполненных по основным полупроводниковым технологиям со сравнимыми топологическими нормами, а в табл. 2 – параметры диэлектрических подложек, применяемых в микроэлектронике СВЧ.

Таким образом, достижение высоких характеристик системы требует применения не одной полупроводниковой технологии, а комбинации ряда полупроводниковых технологий — гетерогенной интеграции. Интеграция двух или более различных полупроводниковых техноло-

*Табл. 1.* Параметры транзисторов на различных полупроводниковых технологиях *Tab. 1.* Parameters of semiconductor technology transistors

| Технология           | Длина затвора<br>(ширина эмиттера),<br>нм | <i>F</i> <sub>T</sub> ,<br>ГГц | $F_{ m max},$ ГГц | Рабочее<br>напряжение<br>с-и (к-э), В | <i>NF</i> <sub>min</sub> , дБ | Ссылка/Компания               |

|----------------------|-------------------------------------------|--------------------------------|-------------------|---------------------------------------|-------------------------------|-------------------------------|

| GaAs pHEMT           | 135                                       | 100                            | 180               | 4.5                                   | 1.1 на 30 ГГц                 | [4] / OMMIC                   |

| InP HEMT             | 100                                       | 180                            | 350               | 1.2                                   | <1 на 40 ГГц                  | [5] / Northrop<br>Grumman     |

| GaN/Si (SiC)<br>HEMT | 100                                       | 100                            | 180               | 12                                    | 1.8 на 40 ГГц                 | [6] / OMMIC                   |

| SiGe<br>БиКМОП       | (120)                                     | 240                            | 280               | (0.6)                                 | 2 на 30 ГГц                   | [7] / STMicro-<br>electronics |

| кни кмоп             | 130                                       | 140                            | 100               | 1.2                                   | 2 на 15 ГГц                   | [8] / IBM                     |

Табл. 2. Характеристики диэлектрических подложек, применяемых в микроэлектронике СВЧ

Таb. 2. Properties of dielectric substrates used in microwave microelectronics

| Параметр                                                                         | Символ             | Сапфир | GaAs  | InP   | Si    | SiC (4H)           | С      | GaN                    |

|----------------------------------------------------------------------------------|--------------------|--------|-------|-------|-------|--------------------|--------|------------------------|

| Ширина<br>запрещенной<br>зоны, эВ                                                | $E_{ m g}$         | 9.5    | 1.42  | 1.34  | 1.12  | 3.25               | 5.46   | 3.44                   |

| Пробивное напряжение, В/мкм                                                      | $E_{ m br}$        | 48     | 40    | 50    | 30    | 400                | 1000   | 500                    |

| Подвижность электронов, см <sup>2</sup> /(B·c)                                   | $\mu_{n}$          | -      | 8500  | 5370  | 1450  | 700                | 2200   | 1000                   |

| Дрейфовая скорость насыщения электронов, ×10 <sup>7</sup> см/с                   | $v_{ m sat}$       | -      | 2.1   | 2.5   | 1     | 2                  | 2.7    | 2.2                    |

| Диэлектрическая проницаемость                                                    | $\epsilon_{\rm r}$ | 9.4    | 12.9  | 12.5  | 11.7  | 9.66               | 5.7    | 8.9                    |

| Тангенс угла диэлектрических потерь                                              | -                  | 0.0001 | 0.006 | 0.008 | 0.015 | 0.003              | 0.0003 | _                      |

| Теплопроводность,<br>Вт/(м·°С)                                                   | Θ                  | 46     | 52    | 68    | 130   | 450                | 1800   | 130                    |

| Коэффициент термического расширения, $\times 10^{-6}  {}^{\circ}\mathrm{C}^{-1}$ | -                  | 4.5    | 5.73  | 4.75  | 2.6   | 5.12               | 1      | a = 5.59,<br>c = 3.17  |

| Постоянная кристаллической решетки, Å                                            | _                  | _      | 5.65  | 5.87  | 5.43  | a = 3.1,<br>b = 10 | 3.57   | a, b = 3.2,<br>c = 5.2 |

гий, обеспечивающая расширение функциональности и улучшенные рабочие характеристики, является актуальной проблемой современной ЭКБ СВЧ. Современный уровень и тенденции развития конструктивных подходов интеграции микроэлектроники СВЧ требуют детального анализа.

В данной статье представлен обзор современных подходов к интеграции разных полупроводниковых технологий для применения в микроэлектронике СВЧ. В работе последовательно описываются 8 методов интеграции: монолитная гетерогенная интеграция; монтаж пластина-к-пластине; метод переноса слоев; интеграция в единую подложку; интеграция методом печати; интеграция проволоками; перевернутый монтаж; hot-via. Рассматриваются конструктивные подходы к интеграции, этапы реализации, достоинства и недостатки.

**Монолитная гетерогенная интеграция.** Монолитная гетерогенная интеграция — интеграция приборов на разных полупроводнико-

вых материалах, электрически соединенных между собой, сформированых в едином технологическом цикле на одной подложке. Этот термин фактически применяется при интеграции различных А<sup>III</sup>В<sup>V</sup>-приборов с Si-КМОП в одной плоскости. Применение монолитной интеграции для объединения широкозонных полупроводниковых приборов с кремниевой КМОП-технологией может обеспечить уменьшение массогабаритных характеристик, сокращение электромагнитных помех, повышение эффективности, производительности и надежности.

Возможность монолитной интеграции  $A^{III}B^V$ -приборов на кремний активно исследуется с 1980-х гг. Исторически, широкозонные полупроводники не изготавливались на кремниевых производственных линейках из-за меньшего диаметра пластин и проблем с загрязнением. Дополнительными сдерживающими факторами являются разница параметров постоянных кристаллических решеток и коэффициентов теплового расширения. Рассогласо-

вание по параметрам постоянных решеток приводит к большому количеству дефектов в растущем слое материала, а также возникновению напряжений вследствие значительного различия коэффициентов линейного расширения. Для минимизации кристаллических дефектов современные кремниевые КМОП-структуры и широкозонные полупроводники A<sup>III</sup>As и A<sup>III</sup>P преимущественно формируются на подложке с кристаллографической ориентацией <100>, когда A<sup>III</sup>N формируется на <111>. Постоянные кристаллических решеток GaAs и InP по сравнению с Si <100> различаются на 4 и 8 % соответственно. GaN имеет 17 %-ю разницу в кристаллической решетке с Si <111>.

На практике возможны 2 основных подхода к интеграции. Первый - интеграция "островков"  $A^{III}B^V$  в проводящую кремниевую подлож- $\kappa_{\rm V}$  <100> [9]. Второй – на подложке кремния на изоляторе (КНИ) формирование Si-КМОП с  $A^{III}B^V$ , выращенными на основной подложке Si <111> [10]. Первый метод минимизирует близкой достоинства интеграции приборов с Si-КМОП для применения в СВЧдиапазоне, так как основная неизолирующая кремниевая подложка оказывает сильный негативный эффект на общие параметры изделия в виде увеличения потерь в линиях передачи и индуктивностях. Необходимость обеспечения дополнительной изоляции А<sup>III</sup>В<sup>V</sup>-приборов с Si-КМОП вносит дополнительные технологические трудности. В связи с этим первый подход применим только для низкочастотных схем.

Обобщенный процесс формирования Si-

КМОП и  $A^{III}B^{V}$ -приборов на единой подложке можно разделить на 6 этапов:

- изготовление требуемой начальной подложки;

- − формирование Si-КМОП;

- формирование окон для  $A^{III}B^{V}$ -приборов;

- эпитаксиальный рост структур;

- − формирование А<sup>Ш</sup>В<sup>V</sup>-приборов;

- формирование металлических межсоединений.

Обычно КМОП-приборы формируются в первую очередь, так как этот процесс является более высокотемпературным, а материалы  $A^{III}B^V$  сильнее восприимчивы к высоким температурам. Рост эпитаксиальных структур на GaAs и InP проходит при температурах более 500 °C, тогда как рост GaN — при 750 °C. Данные температуры существенно влияют и на характеристики КМОП-транзисторов. Таким образом, взаимное влияние технологического процесса изготовления приборов Si-КМОП и  $A^{III}B^V$  является важной проблемой, ограничивающей применение данного метода интеграции.

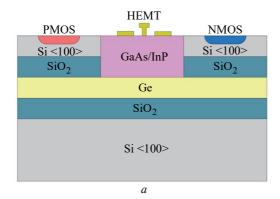

Формирование структур на GaAs и InP на единой Si-подложке было продемонтстрировано с применением пластины SOLES (Soitec's Silicon On Lattice Engineered Substrate). Типичная структура приведена на рис. 1, а. Формирование структуры на GaAs требует применения подслоя Ge для минимизации рассогласованности кристаллических решеток. Формирование структур на InP, помимо подслоя Ge, требует применения буферного слоя GaAs. Ge как подслой получил наибольшее распространение,

Puc.~1. Схематичное представление монолитной гетерогенной интеграции:  $a-{

m Si\text{--}KMO\Pi}$  и GaAs/InP HEMT (либо ГБТ) на SOLES;  $\delta-{

m Si\text{--}KMO\Pi}$  и GaN HEMT на SOI

Fig. 1. Schematic representation of monolithic heterogeneous integration: a-Si-CMOS with GaAs/InP HEMT (or HBT) on SOLES;  $\delta-\text{Si-CMOS}$  and GaN HEMT on SOI

поскольку характеризуется хорошей смешиваемостью с Si, обладает зрелой технологией выращивания Ge-on-Si и имеет схожие значения постоянной кристаллической решетки с GaAs. Буферный слой  $Ge_xSi_{1-x}$  обеспечивает эффективную релаксацию. Верхний слой Ge служит виртуальной подложкой для дальнейшего роста GaAs.

Реализация данного подхода не нашла широкого применения ввиду некоторых технологических ограничений. Так, промежуточный слой Ge имеет температуру плавления 938 °C, что ограничивает диапазон температур при изготовлении КМОП на кремнии. Также Ge вызывает перекрестное легирование с GaAs, что ухудшает характеристики GaAs pHEMT [11]. Буферные слои большой толщины являются ограничением для планаризации конструкции. Начальная подложка, необходимая для формирования требуемой полупроводниковой структуры, на сегодняшний день является предметом ограниченного распространения с крайне высокой стоимостью [12].

Интеграция структур на GaN имеет предпосылки к внедрению в цепочку производства кремниевых схем. GaN является химически стабильным во всем температурном диапазоне, применяемом в производстве кремниевых КМОП. Возможное совмещение процессов на 200 мм кремниевых пластинах, где технология GaN на кремнии интегрирована со стандартной технологией изготовления КМОП, может быть применена как для области высоких частот, так и для силовой электроники. Типичная структура интеграции приборов на GaN и Si-КМОП представлена на рис. 1, б. GaN и кремниевые транзисторы интегрированы не вертикально, а в единой плоскости. Одними из первых данный подход был реализован группой из Raytheon [13]. Немаловажным недостатком данного подхода является высокая стоимость ввиду селективного роста эпитаксиальных слоев, обеспечивающегося методом молекулярно-лучевой эпитаксии. Несмотря на то, что в типичной интегральной схеме всего 10 % площади занимает GaN HEMT, цена процесса эпитаксии идентична со всей пластиной. Следовательно, таком подходе стоимость площади GaN-структуры в 10 раз больше.

За последние 30 лет наблюдался значительный прогресс в интеграции A<sup>III</sup>B<sup>V</sup>-приборов и Si-38

КМОП на единой кремниевой подложке. Данный подход гетерогенной интеграции, обладающий минимальными длинами межсоединений и массогабаритными характеристиками, обеспечит новый класс схем с высокими характеристиками, объединяя цифровую обработку, смешение сигналов и аналоговое преобразование. Это расширяет возможности существующих систем и делает возможным новые архитектуры для широкого перечня применений. Отдельной перспективной областью для приборов с повышенными характеристиками для радиоэлектронной аппаратуры нового поколения является применение алмазной диэлектрической подложки и интеграция на ней разных полупроводниковых структур: Si-КМОП и GaN HEMT [14].

Однако, несмотря на заметное технологическое продвижение в монолитной интеграции  $A^{III}B^{V}$ -приборов на кремниевую подложку и конструктивные преимущества, данный подход остается лишь одним из потенциальных направлений развития будущей микроэлектроники СВЧ. Важными предпосылками, требуемыми для практического применения данного подхода, станет решение ряда фундаментальных проблем, связанных с разницей в значениях постоянных кристаллических решеток, коэффициентов температурного расширения [15]. Требуется уменьшение взаимного влияния технологического процесса изготовления схемы на КМОП- и  $A^{III}B^{V}$ -приборы. Помимо этого метод должен быть экономически конкурентным с аналогичными подходами гетерогенной интеграции.

Монтаж пластина-к-пластине. Монтаж пластина-к-пластине (wafer bonding) – процесс интеграции изделий на уровне изготовления пластин посредством соединения пластин со сформированными приборами. Данный подход является альтернативным к монолитной интеграции.

Обобщенный процесс объединения состоит из двух основных этапов. На первом этапе соединяются друг с другом две пластины со сформированными активными элементами. Соединение двух пластин обеспечивается за счет металлических или диэлектрических слоев, либо их совокупности – гибридного монтажа (hybrid bonding) [16]. На втором этапе формируются отверстия как в одной, так и в другой пластинах, финальная металлизация, объединяющая элементы.

Важными условиями интеграции данным методом являются одинаковые размеры соединяемых пластин, применение соединяющих металлических либо диэлектрических слоев, совместимых с двумя интегрируемыми полупроводниковыми технологиями, и обеспечение шероховатости поверхностей менее 1 нм [17, 18]. Для планаризации соединяемых поверхностей необходима химико-механическая полировка. Совместимость технологических процессов соединяемых пластин составляет одну из основных задач, решение которой необходимо для реализации данного подхода. Совместимость с технологическим процессом Si-КМОП подразумевает отказ от использования Аи и процессов взрывной литографии – укоренившихся составляющих технологического процесса производства  $A^{III}B^{V}$ приборов.

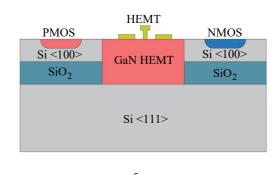

Структуры на основе GaN имеют наибольшие предпосылки интеграции методом монтажа пластина-к-пластине благодаря высокотемпературной стабильности приборов на их основе. Также появилась возможность реализации GaN-гетероструктур на пластинах высокоомного кремния диаметром 200 мм [17]. Группа из Raytheon ведет работы по реализации пластины GaN на Si, изготовленной в кремниевой технологической цепочке, и последующей интеграции с пластиной Si-КМОП [19]. Схематичное представление реализуемой концепции представлено на рис. 2.

Выходные характеристики экспериментальных образцов GaN HEMT на кремниевой подложке, изготовленных по технологической цепочке без процессов взрывной литографии и использования Au, показывают сопоставимые значения со стандартными приборами. Выход-

ная мощность тестовых транзисторов  $2 \times 100$  мкм с длиной затвора 0.15 мкм превышает 4.5 Вт/мм при КПД  $50\,\%$  на частоте  $10\,\Gamma\Gamma$ ц. Электрическое соединение между GaN НЕМТ и Si-КМОП обеспечивается сквозными металлизированными отверстиями в Si. Металлизация выполнена из Cu.

Также имеются экспериментальные результаты по интеграции пластина-к-пластине приборов на InP с Si-КМОП. В [18, 20] представлены результаты интеграции InP ГБТ с Si-КМОП или БиКМОП. Благодаря плотной интеграции разных полупроводниковых приборов реализованы приемопередатчики Ка- и W-диапазонов частот в виде единого кристалла, где реализованы как цифровая, так и аналоговая части.

Монтаж пластина-к-пластине обеспечивает высокую плотность интеграции и минимальные габариты благодаря вертикальной интеграции приборов. Недостатками данного подхода являются как снижение процента выхода годных из-за концепции монтажа пластина-кпластине, так и ограничение в диаметре пластин (до 100 или 150 мм) при интеграции с большинством пластин с А<sup>III</sup>В<sup>V</sup>-приборами. Совместимость технологических процессов также является важным фактором, сдерживающим массовое внедрение данного подхода. Кроме того, при гетерогенной интеграции наблюдается неэкономичное использование пластины с А<sup>III</sup>В<sup>V</sup>-приборами. Данный подход экономически целесообразен при высоком проценте А<sup>III</sup>В<sup>V</sup>-приборов в финальной интеграции, поэтому он наиболее применим при интеграции пластин, реализованных по единой технологии. Гетероинтеграция в данном подходе предусматривает совместимость ряда этапов

Рис. 2. Схематичное представление интеграции пластины GaN HEMT на кремнии с пластиной Si-KMOП [19]

Fig. 2. Schematic representation of wafer bonding GaN HEMT on Si with Si-CMOS [19]

производства соединяемых пластин, что зачастую требует корректировки части технологических процессов.

Метод переноса слоев. Метод переноса слоев (micro-transfer printing) – технология локального переноса определенных полупроводниковых слоев с одной подложки (донорной) на финальную пластину. Данная технология позволяет интегрировать приборы, реализованные на материалах с несовпадающими показателями кристаллических решеток, расширяя функциональность и повышая характеристики, компактно объединяя разные полупроводниковые материалы.

Гетероструктуры А<sup>III</sup>В<sup>V</sup> содержат весь необходимый функционал, требуемый для работы активного прибора СВЧ. Отделение структуры от подложки и ее перенос является стремлением к увеличению плотности интеграции разных полупроводниковых приборов, минимизации лишних элементов. Метод переноса слоев активно применяется в полупроводниковой фотонике [21].

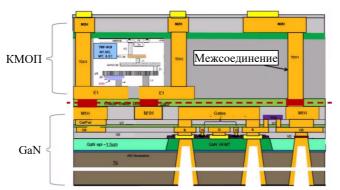

Обобщенный принцип реализации метода переноса слоев можно разделить на 6 основных этапов. Схематичное представление процессов представлено на рис. 3. Изготавливается донорная пластина с требуемыми элементами. Первым этапом является формирование локальных областей структур на донорной пластине. Далее локально наносится защитный слой, который в дальнейшем будет обеспечивать контакт с трафаретом и остаточный контакт с донорной пластиной. Защитным слоем может служить либо фоторезист, либо диэлектрик. Третий этап – отсоединение структур от подложки. Существует

несколько способов отсоединения: селективным травлением; лазерным; ионным; либо механическим воздействием [22, 23]. Четвертый и пятый этапы – перенос элементов с донорной пластины на финальную с помощью трафарета. Разработан целый ряд подходов к переносу элементов, наиболее применяемым из которых является использование эластомера из полидиметилсилоксана. По причине высокой адгезии трафарета и переносимого прибора при резком движении трафарета с места контактирования с прибором соединения с донорной пластиной рвутся, позволяя поднять прибор с донорной пластины. Противоположный подход используется для интеграции прибора на финальную пластину, трафарет плавно отодвигается от соединенной поверхности, обеспечивая меньшую адгезию между трафаретом и прибором, чем силы сцепления с финальной подложкой. Шестой этап – удаление защитного слоя. После процесса переноса электрические соединения добавляются стандартными технологическими процессами с применением тонкопленочного напыления и фотолитографии.

Структуры на GaN имеют предпосылки для интеграции методом переноса слоев — изменение в составе материалов от кремния до последовательности гетероструктур на GaN позволяет легко убирать лежащий внизу кремний анизотропным травлением. Текущие экспериментальные результаты по интеграции GaN HEMT на кремниевую пластину с реализованной КМОП пока применимы больше для силовой электроники [24]. Метод переноса слоев при-

Рис. 3. Схематичное представление процесса микропереноса слоев

Fig. 3. Schematic representation of micro-transfer printing process

влекателен в том случае, когда монолитная интеграция либо затруднительна, либо невозможна. Так, в [25] приведены экспериментальные результаты интеграции GaN HEMT на алмазную подложку. Также имеются экспериментальные данные по применению данного подхода для интеграции InP HBT на кремниевую пластину [18].

Интеграция методом переноса слоев является потенциальным подходом к интеграции приборов, выполненных по разным полупроводниковым технологиям. Метод переноса слоев выступает в качестве конкурирующего подхода с монолитной гетероинтеграцией. Достоинствами данного подхода являются минимальные длины межсоединений между приборами на разных материалах и массогабаритные характеристики, эффективное использование донорной пластины. Подобный метод может найти широкое применение при необходимости переноса большого массива элементов для быстрого монтажа миниатюрных элементов. Недостатки данного подхода включают необходимость связи минимум двух разных полупроводниковых процессов, ограниченные размеры переносимого объекта – около  $0.6 \times 0.6$  мм, а также проблемы с планарностью при больших толщинах гетероструктур.

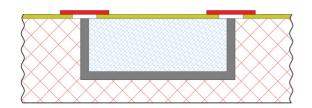

Интеграция в единую подложку. Метод интеграции в подложку предполагает, что на основную полупроводниковую пластину, в местах углублений, интегрируются готовые кристаллы элементов, в дальнейшем соединяемые друг с другом с применением методов фотолитографии (рис. 4). Данный метод в разных источниках имеет различные названия: interposerbased monolithic microwave integrated circuit (iMMIC) [26]; quasi-monolithic integration technology (QMIT) [27]; metal embedded chip assem-

Рис. 4. Схематичное представление интеграции в подложку Fig. 4. Schematic representation of embedded chip assembly method

bly for microwave integrated circuits (MECAM-IC) [2, 28]; embedded-IC package [29].

Данный подход является развитием традиционной концепции ГМИС с проволочными соединениями - использование готовых кристаллов активных элементов (транзисторов и МИС), их интеграция с кристаллами пассивных элементов проволочными соединениями. Интеграция в подложку обеспечивает избавление от проволочных соединений, тем самым уменьшая электрические паразитные характеристики межсоединений и снижая габаритные характеристики. Применение готовых кристаллов активных элементов и их интеграция с пассивными частями обеспечивают уменьшение стоимости однофункциональных схем, например усилителей мощности на GaN HEMT, в связи с тем, что дорогостоящий кристалл со структурами GaN на подложке SiC ограничен активным прибором, а пассивная часть реализуется монолитно на более дешевых подложках полуизолирующих GaAs или Si.

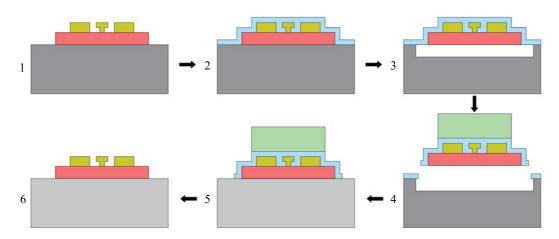

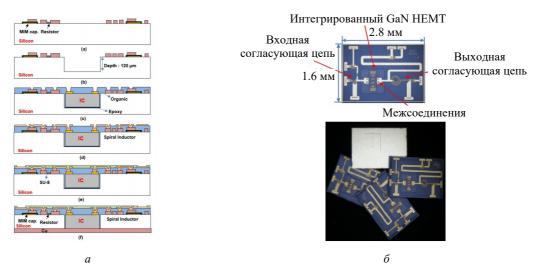

Процесс интеграции в подложку обеспечивается на этапе производства обобщающей пластины. В обобщающей подложке формируется полость для размещения готового кристалла. Соединение кристалла с обобщающей подложкой обеспечивается стандартными технологическими процессами изготовления обобщающей подложки с применением тонкопленочного напыления и фотолитографии. В [2, 26, 28] представлены результаты реализации усилителей мощности S-, X- и W-диапазонов частот, где в кремниевую полуизолирующую подложку с пассивными элементами интегрирован кристалл GaN-транзистора. Представленные усилители имеют повышенный уровень интеграции в совокупности с эффективным использованием дорогостоящих кристаллов активных элементов на гетероструктурах в сочетании с пассивными платами на полуизолирующих подложках, объединенных на уровне изготовления пластины с пассивными платами. Типичный процесс интеграции и фотографии усилителей представлены на рис. 5.

Частный случай интеграции в подложку — metal-embedded chip assembly (MECA) (бывший Integrated thermal array plate (ITAP)) — метод интеграции в подложку, обеспечивающий

Рис. 5. Типичный процесс интеграции в подложку (a) и фотографии изготовленных усилителей мощности X-диапазона частот ( $\delta$ ) [26]

Fig. 5. Typical embedded chip assembly fabrication process (a) and fabricated X-band power amplifier (δ) [26]

повышенные тепловые характеристики. Данный подход подразумевает интеграцию кристаллов в медный теплоотвод, который имеет одинаковую толщину с кремниевой распределительной платой. Контакт между обратной стороной кристаллов и теплоотводом без соединяющего слоя улучшает тепловые характеристики по сравнению с традиционными методами. Межсоединения, реализованные воздушными мостами между кристаллами и платами, заменяют проволочные соединения и обеспечивают минимальное расстояние между кристаллами 70 мкм с возможностью его уменьшения до 30 при дальнейшей оптимизации процесса [30]. Данный метод подразумевает использование кремниевых пластин большого диаметра.

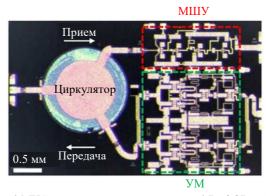

Метод интеграции в подложку позволяет объединять не только полупроводниковые кристаллы, но и другие приборы, применяемые в микроэлектронике СВЧ. Одним из перспективных направлений применения данного метода является близкая интеграция ферритовых изделий с МИС СВЧ. В [31] представлены результаты интеграции циркулятора из поликристаллического гексаферритного магнитного материала с приемопередающим модулем СВЧ, состоящим из малошумящего усилителя (МШУ) и усилителя мощности (УМ) на GaN/SiC на уровне пластины, фотография которого представлена на рис. 6. Результатом является ГМИС приемопередатчика Ка-диапазона частот, в ко-

Puc.~6.~ МИС приемопередатчика размером  $4.7 \times 2.87~$  мм [31] Fig.~6.~ T-R MMIC with chip size of  $4.7 \times 2.87~$  mm [31]

торую интегрирован циркулятор. Это обеспечивает снижение габаритов больше чем в 100 раз в сравнении с традиционным подходом.

Метод интеграции в подложку находит все более широкое применение при построении как однофункциональных, так и многофункциональных схем СВЧ с малыми габаритными характеристиками. Реализация концепции ГМИС – использование годных кристаллов и пассивных плат на полуизолирующих подложках — способствует снижению стоимости конечных изделий и обеспечивает повышение процента выхода годных. Достоинствами данного подхода являются планарность полученной интеграции, экономичное использование площади кристаллов с гетероструктурами и небольшие паразитные составляющие переходных межсоединений в СВЧ-диапазоне. Различные варианты реали-

зации данного подхода могут обеспечить повышенные тепловые характеристики, интеграцию неполупроводниковых материалов. Недостатки — необходимость применения полупроводниковых технологических этапов, что ведет к повышенной сложности технологических процессов интеграции. Рассматриваемый подход предъявляет повышенные требования к повторяемости габаритных размеров кристаллов, точности их позиционирования.

Интеграция методом печати. Интеграция методом печати - электрическое соединение отдельных кристаллов с подложкой с применением аддитивных технологий. Аддитивные технологии могут быть использованы для создания линий передачи, антенн, кристальных межсоединений, соединительных и изолирующих слоев и 3D-конструкций [32]. Одним из основных стимулов развития данного подхода является снижение паразитных характеристик межсоединений с целью улучшения характеристик модулей в миллиметровом диапазоне частот. Развитие методов аддитивных технологий, основанных на микродозировании с возможной последующей обработкой, позволило формировать линии шириной до 10 мкм с точностью  $\pm 6$  мкм [33].

Интеграция методом печати позволяет изготавливать многокристальные модули с быстрым этапом макетирования и возможностью оптимизации конструкции. На рис. 7 представлен результат реализации приемопередатчика W-диапазона с применением аддитивных технологий [33]. Перспективным направлением

Рис. 7. Приемопередатчик W-диапазона, реализованный с применением аддитивных технологий [33]

Fig. 7. Fabricated W-band transceiver implemented using additive technologies [33]

применения аддитивных технологий является формирование 3D-антенн для миллиметрового диапазона длин волн [34].

Достоинством данного подхода является возможность автоматизации и скорость разработки модулей, упрощение процессов интеграции, так как не требуется использования полупроводниковых технологических процессов. Однако данный подход не может похвастаться большими производственными мощностями, как и исключительными электрическими параметрами ввиду ограниченных технологических возможностей формирования межсоединений. Также необходима отдельная дорогостоящая автоматизированная платформа для интеграции.

Метод интеграции с применением аддитивных технологий не имеет на данный момент очевидных преимуществ по сравнению с конкурентными методами интеграции, однако у него большие перспективы с точки зрения автоматизированной интеграции мелкосерийного производства.

Интеграция проволоками. Проволочный метод интеграции кристаллов - механическое соединение кристаллов на основании с помощью вспомогательного соединяющего слоя и электрическое соединение проволоками. Концепция интеграции кристалла на подложку проволочным методом представлена на рис. 8. Электрическое соединение кристалла с подложкой проволоками является зрелым процессом и превалирует в современном процессе сборки кристаллов СВЧ. Обычно тонкие металлические проволоки диаметром 15...25 мкм соединяют контактные площадки кристалла и основания. Обратная сторона кристалла монтируется к основанию с помощью соединяющего слоя.

*Puc.* 8. Проволочный метод интеграции кристаллов *Fig.* 8. Schematic representation of wire bond integration

Главное достоинство данного подхода — его простота, зрелость и распространенность технологии, небольшие требования к плоскопараллельности и шероховатости кристалла и основания, невысокая стоимость. Интеграция проволоками применяется при построении как однофункциональных схем, их корпусировании, так и интеграции МИС в многофункциональную систему [35].

В [36] показан пример реализации усилителя мощности Х-диапазона частот, где кристалл GaN-on-Si с предусилителем и выходными транзисторами интегрирован золотыми проволоками с кристаллом выходной согласующей цепочкой полуизолирующем арсениде галлия (рис. 9). Разработанный усилитель имеет выходную мощность свыше 18 Вт при коэффициенте усиления более 27 дБ в диапазоне частот 9.5...11.5 ГГц. Его габаритные размеры  $5.5 \times 3.8$  мм, а расчетная стоимость в 2 раза ниже по сравнению с усилителем, реализованным на едином кристалле на GaN-on-SiC.

Подобная технология монтажа трудоемка, так как соединения между кристаллом и подложкой делаются последовательно. Для кристаллов с большим количеством выводов процесс может оказаться достаточно длительным. Плотность выводов кристалла ограниченна, так как они в данном случае являются периферийными элементами схемы. Контактные площадки для интеграции проволоками занимают большую площадь на кристалле, а последовательный планарный контакт монолитных схем ограничивает

Рис. 9. УМ X-диапазона частот с GaAs-платой выходной согласующей цепи [36]

Fig. 9. X-band power amplifier with GaAs MMIC output matching circuit [36]

минимальные габаритные характеристики модуля СВЧ.

Современные методы механического контакта обратной стороны кристаллов с основанием вносят существенный вклад в тепловое сопротивление сборки, ухудшая тепловые режимы работы схемы, что снижает надежность, так как подразумевает применение клея либо припоя с толщиной около 20 мкм и невысокой теплопроводностью (50...60 Вт/(м·К)).

Еще один важный недостаток проволочных соединений – ухудшение характеристик на высоких частотах ввиду значительных паразитных составляющих. Это является ключевой проблемой для интеграции схем, работающих в миллиметровом диапазоне длин волн. Главная паразитная составляющая проволок - индуктивность, которая увеличивается пропорционально длине межсоединения. Частотные характеристики ограничены, так как паразитные составляющие переходных межсоединений вносят искажения, которые невозможно компенсировать идеальными сосредоточенными элементами уже на 40 ГГц, что является худшим результатом среди подходов к интеграции [37]. Длинные проволочные соединения являются источниками излучения, повышающими электромагнитные связи, что ухудшает изоляцию и может стать причиной нестабильности схемы.

Несмотря на то, что на данный момент проволочный метод является основой современной интеграции в микроэлектронике СВЧ, его пределы по частотным характеристикам и плотности интеграции ограничивают получение максимальных характеристик от МИС СВЧ.

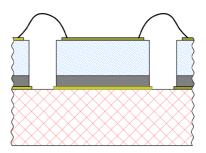

Перевернутый монтаж. Интеграция кристаллов методом перевернутого монтажа (flipchip) — соединение кристалла активной лицевой стороной с подложкой механически и электрически, используя проводящие межсоединения — "бампы". Концепция интеграции кристалла на подложку методом перевернутого монтажа представлена на рис. 10. Актуальность данного подхода определяется развитием широкополосной радиоэлектронной аппаратуры миллиметрового диапазона длин волн, концепции ГМИС в области миниатюризации и гетероинтеграции и технологии формирования

Puc. 10. Концепция интеграции кристалла методом перевернутого монтажа

Fig. 10. Schematic representation of flip-chip integration

переходных межсоединений, обеспечивающей миниатюризацию и совместимость с технологией изготовления  $A^{III}B^{V}$ -кристаллов. Интеграция методом перевернутого монтажа обеспечивает одновременное соединение между большим количеством контактных площадок основания и кристалла, минимальные потери и паразитные составляющие переходных межсоединений в СВЧ-диапазоне, а в перспективе и улучшенный теплоотвод от активной области прибора.

Начало развития технологии flip-chip относится к 1964 г., когда компания IBM разработала технологию C4 (Controlled Collapse Chip Connection) для сборки интегральных схем. Технология flip-chip стала важной частью в цифровой микроэлектронике, тогда как в СВЧобласти не нашла широкого распространения. Одна из причин состоит в том, что типичная технология flip-chip не может быть перенесена для применения в СВЧ-области. Способ формирования переходных межсоединений – "бампов", их высота, диаметр и применяемые материалы требуют изменения для стыковки с тех-

нологией МИС СВЧ, выполненных на широкозонных полупроводниках, миниатюризации и обеспечения низких паразитных электрических составляющих в СВЧ-диапазоне [38].

Обобщенный процесс монтажа методом flipсһір состоит из трех основных этапов. Первый – формирование проводящих межсоединений ("бампов") на контактных площадках кристалла или подложки. Второй - монтаж, совмещение кристалла с подложкой и соединение первого лицом вниз при заданных внешних условиях (температура, время и давление). Третий – заполнение вспомогательным материалом пустот между кристаллом и подложкой – инкапсуляция. Последняя обеспечивает улучшение термомеханических свойств, вызванных несоответствием КТР кристалла и подложки, а также защищает кристалл от влаги, загрязнений и механических повреждений при различных внешних факторах. Однако присутствие вспомогательного материала влияет на электрические характеристики системы, особенно на высоких частотах, в связи с его более высокими диэлектрической проницаемостью и тангенсом угла диэлектрических потерь в сравнении с воздухом. Третий этап в отдельных случаях может быть опущен, особенно в схемах миллиметрового диапазона длин волн.

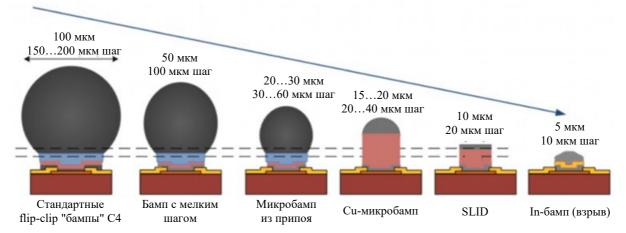

Бурное развитие способов формирования "бампов", способствующее миниатюризации, повышению рабочего диапазона температур и надежности переходных межсоединений и сборок на их основе, открывает новые возможности применения метода перевернутого монтажа. Схематичное представление эволюции переходных межсоединений иллюстрирует рис. 11.

Рис. 11. Схематичное представление эволюции переходных межсоединений [39]

Fig. 11. Schematic representation of bump interconnect evolution [39]

Технология формирования проводящих межсоединений развивается более 60 лет. В общем, данный процесс можно разделить на 3 поколения. Первое поколение подразумевает использование шариков припоя и флюса. Типичный размер межсоединений первого поколения обеспечивает шаг между выводами более 100 мкм. Второе поколение, часто именуемое как micro-bump или C2 (chip connection), реализуется как контактная площадка из меди, покрытая припоем; обеспечивает шаг между выводами от 40 до 130 мкм. Первые 2 поколения имеют значительный объем легкосплавных припоев в межсоединении. Их присутствие ограничивает область применения радиоэлектронной аппаратуры из-за уменьшения рабочего температурного диапазона [40].

Третье поколение межсоединений обеспечивает шаг между выводами 30 мкм и менее. Существующие процессы с использованием припоев не могут обеспечить масштабирование межсоединений до указанных размеров. В связи с этим для реализации межсоединений с отмеченными размерами применяются методы термокомпрессии Си-Си [41], Аи-Аи [42] либо метод монтажа взаимной переходной диффузией **SLID** (англ. сокр. Solid-Liquid Interdiffusion) с разными составляющими материалами [43]. Ведутся работы по созданию переходных межсоединений, обеспечивающих широкополосное соединение с рабочей полосой свыше 150 ГГц и интеграцию, близкую к монолитной [38, 44, 45]. Технология реализации переходных межсоединений с возможностью локального контакта кристаллов с шагом в единицы микрометров до сих пор является актуальной задачей в микроэлектронике СВЧ.

Интеграция методом перевернутого монтажа все шире применяется в маломощных системах миллиметрового диапазона благодаря таким преимуществам, как минимальные потери и паразитные составляющие соединений (не требуется компенсирующих согласующих элементов) и относительная простота технологии [46], а в X-диапазоне показывают улучшенные характеристики по сравнению с распространенным методом монтажа с помощью проволочных соединений [47]. Достоинством концепции интеграции методом перевернутого монтажа является возможность использования

кристаллов, выполненных по разным технологическим процессам.

На текущей момент метод перевернутого монтажа имеет ряд ограничений. Монтаж методом flip-chip приводит к близкому расположению активной поверхности кристалла с подложкой, которые разделены воздушным зазором в высоту переходного межсоединения. Подобная близость существенно влияет на электрические характеристики кристалла. Данное явление называется эффектом рассогласования. Элементы схемы на кристалле могут изменить свои электрические характеристики в связи с присутствием подложки в непосредственной близости. Степень рассогласования зависит от типа элемента и размера зазора между кристаллом и подложкой, который контролируется высотой бампа. Присутствие металлизации под кристаллом сильно увеличивает эффект [48]. Большая высота бампа минимизирует рассогласование, однако увеличивает паразитные характеристики переходного соединения. На практике чувствительны к эффекту рассогласования линии передачи и спиральные индуктивности, в то время как транзисторы и компоненты малых размеров не отличаются значительной восприимчивостью. В связи с этим интеграция кристаллов с реализованной микрополосковой конструкцией требует детального просчета и учета данного эффекта.

Еще одной актуальной проблемой при интеграции методом перевернутого монтажа является отвод тепла. Концепция контакта кристалла лицевой стороной при методе перевернутого монтажа обеспечивает кратчайший электрический путь соединения с основанием, однако ограниченная площадь контакта (обычно менее 10% от площади кристалла) и его удаленность от области тепловыделения увеличивают тепловое сопротивление схемы, что ведет к повышенным температурным режимам работы и, как следствие, к снижению электрических характеристик и надежности схемы.

Один из способов улучшения отвода тепла — использование обратной стороны кристалла, ее контакт с высокотеплопроводным материалом. В [49] представлены экспериментальные данные применения указанного подхода, где в предложенной конструкции корпусирования

кристалл усилителя мощности, реализованного на 0.25 мкм GaN HEMT-технологии, монтируется лицевой стороной на подложку, а обратная сторона контактирует с медным теплоотводом. Рассеиваемая мощность в эксперименте от МИС СВЧ-усилителя размером 5.0 × 2.5 мм составила от 6 до 20 Вт. Интеграция кристалла внесла минимальные искажения в частотные характеристики схемы в диапазоне 0...14 ГГц, однако, несмотря на присутствие дополнительного отвода тепла от обратной стороны кристалла, наблюдается повышение рабочего температурного режима, что свидетельствует о необходимости дальнейшего совершенствования конструкции. Другой способ повышения отвода тепла – увеличение площади контактирования лицевой стороны кристалла с подложкой в области, близкой к области тепловыделения. Результаты расчета показывают, что возможно даже улучшение температурных режимов, по сравнению с традиционным методом интеграции кристалла обратной стороной на теплоотводящее основание [50, 51]. Данный подход требователен к точности формирования соединяющих слоев, их размеров и к точности совмещения, что еще раз подчеркивает актуальность технологии реализации переходных межсоединений с возможностью локального контакта кристаллов с шагом в единицы микрометров.

Интеграция методом перевернутого монтажа на сегодняшний день является наиболее быстроразвивающимся подходом в области построения СВЧ-модулей на основе гибридномонолитной интеграции. Такие достоинства подхода, как минимальные потери и паразитные составляющие переходных межсоединений в СВЧ-диапазоне [1], возможность использования готовых кристаллов, реализованных по разным полупроводниковым технологиям и с разными габаритами, одновременное соединение большого количества контактных площадок кристалла с основанием, возможность монтажа на уровне пластины и плотность интеграции, близкая к монолитной, позволяют реализовывать компактные радиоэлектронные модули миллиметрового диапазона частот [52]. Недостатки данного подхода – эффект рассогласования, существующие ограничения по тепловому режиму и повышение требований к плоскопараллельности и шероховатости поверхностей кристаллов и оснований при переходе к размерам межсоединений менее 20 мкм — остаются теми факторами, которые замедляют масштабное применение метода перевернутого монтажа в микроэлектронике СВЧ. Актуальными проблемами данной конструкции остаются улучшение отвода тепла от активной области и технология реализации переходных межсоединений с возможностью локального контакта кристаллов с шагом в единицы микрометров.

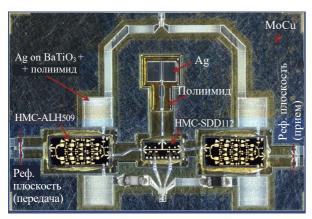

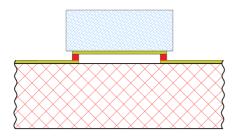

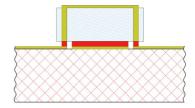

Hot-via. Интеграция кристаллов методом перевернутого монтажа больше применима для схем с копланарными линиями, чем с микрополосковыми, в связи с появлением эффекта рассогласования из-за близости кристалла с подложкой. Однако в большинстве современных ИС применяются именно микрополосковые линии, как наиболее подходящие для мощных схем. Модифицированная конструкция перевернутого монтажа ("hotvia" или "direct backside interconnect technology" (DBIT) – технология прямого соединения обратной стороной) была предложена в конце XX в. как альтернатива технологии перевернутого монтажа, совместимая с конструкцией микрополосковых линий [53]. Концепция данного подхода представлена на рис. 12.

Электрические выводы кристалла выведены на обратную сторону через сквозные металлизированные отверстия (так называемые hotvia). Металлизация обратной стороны должна иметь требуемую топологию, что повышает сложность изготовления схемы. Кристалл схемы соединяется обратной стороной с основанием с помощью либо бампов, либо соединяющего слоя, например фольги припоя. Метод монтажа hot-via обеспечивает одновременно электрическое, тепловое и механическое повторяемое соединение. Процесс интеграции состоит из тех же этапов, что и при перевернутом монтаже. Возможность реализации подоб-

*Рис.* 12. Концепция интеграции кристалла методом hot-via

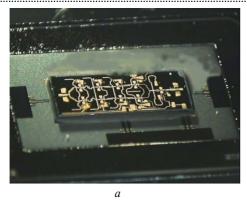

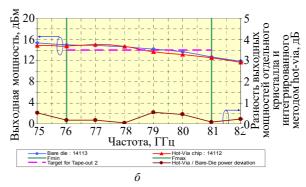

*Puc. 13.* Фотография интегрированной МИС УМ W-диапазона частот (*a*) и частотные характеристики (*δ*) [55] *Fig. 13.* Photograph of integrated W-band PA MMIC (*a*) and electrical characteristics (*δ*) [55]

ной конструкции в СВЧ-диапазоне является следствием развития технологии формирования локальных проводящих межсоединений.

В миллиметровом диапазоне частот форма сигнального сквозного отверстия сильно влияет на характеристики электрического соединения. Например, сигнальное сквозное отверстие в виде квадрата со стороной 35 мкм в подложке толщиной 100 мкм имеет индуктивность около 40 пГн до частот 100 ГГц с тенденцией дальнейшего увеличения [54]. Практическое ограничение применения данного подхода по частотному диапазону составляет около 90 ГГц.

В [55] продемонстрирована интеграция ряда кристаллов для приемопередающего модуля W-диапазона частот. Фотография результатов интеграции и частотные характеристики представлены на рис. 13. Кристалл усилителя мощности, реализованного по технологии GaAs 0.15 рНЕМТ, интегрирован на кремниевую подложку. Соединяющие бампы из золота высотой около 45 мкм формируются на уровне пластины до резки на кристаллы, пустоты заполняются проводящим адгезивом. В диапазоне частот 76...81 ГГц усилитель имеет почти идентичную выходную мощность более 12 дБм как отдельного кристалла, так и интегрированного на подложку. Отсутствие сильных различий определяется использованием компенсирующих цепочек согласования на кристалле для применения интеграции методом hot-via.

Метод интеграции hot-via, как модификация метода перевернутого монтажа, имеет ряд достоинств по сравнению с перевернутым монтажом: лучшую совместимость с микрополосковым построением схем; возможность визуально-

го контроля после монтажа; отсутствие эффекта рассогласования. Однако подход hot-via не лишен недостатков: требуется формирование сигнальных сквозных отверстий, а обратная сторона должна иметь локальную металлизацию для разделения заземления и сигнальных контактных площадок; паразитные параметры межсоединения выше, чем у интеграции перевернутым монтажом, так как сквозное отверстие является частью пути сигнала.

Из-за специфических дополнительных технологических требований к кристаллам и повышенных паразитных составляющих переходных межсоединений данный подход имеет ограниченную область применения. Его дальнейшее совершенствование, как и метода перевернутого монтажа, во многом зависит от развития технологии формирования локальных переходных межсоединений.

Выводы. Целью данной статьи являлось проанализировать современные и перспективные направления конструктивных решений интеграции микроэлектроники СВЧ на основе разных полупроводниковых технологий. Развитие конструкций идет в области снижения межсоединений, уменьшения габаритов, повышения тепловых характеристик, повышения вариативности, снижения себестоимости. В табл. 3 представлены результаты сравнения исследованных методов интеграции.

Традиционный подход к интеграции — проволочный — имеет ограничения по рабочим частотам и приводит к относительно большим габаритам. Развитие подходов интеграции, обеспечивающих повышение функциональности и улучшенные рабочие характеристики, является

Табл. 3. Результаты сравнения характеристик методов интеграции

| Tah 3 Results   | s of comparis | on of integration | methods |

|-----------------|---------------|-------------------|---------|

| Tuo. J. Ixesuna | o or compans  | on or micgianor   | memous  |

| Метод интеграции                         | Минимальная<br>длина<br>межсоединений | Концепция<br>ГМИС | Интегрирующая<br>подложка | Требования для реализации                                                      |

|------------------------------------------|---------------------------------------|-------------------|---------------------------|--------------------------------------------------------------------------------|

| Монолитная<br>гетерогенная<br>интеграция | >5 мкм                                | _                 | Si                        | Совместимость технологических циклов минимум двух полупроводниковых технологий |

| Монтаж пластина-к-<br>пластине           | >5 мкм                                | _                 | Si                        | Совместимость технологических циклов минимум двух полупроводниковых технологий |

| Метод переноса слоев                     | >5 мкм                                | +                 | Любая                     | Совместимость технологических циклов минимум двух полупроводниковых технологий |

| Интеграция в единую подложку             | >70 мкм                               | +                 | Si/SiC/GaAs/C             | Применение технологических этапов. Точное позиционирование                     |

| Интеграция методом печати                | >100 мкм                              | +                 | Любая                     | Автоматизированная платформа<br>для интеграции                                 |

| Интеграция<br>проволоками                | >300 мкм                              | +                 | Любая                     | Нет                                                                            |

| Перевернутый монтаж                      | >5 MKM                                | +                 | Любая                     | Локальный соединяющий слой                                                     |

| Hot-via                                  | >75 MKM                               | +                 | Любая                     | Локальный соединяющий слой                                                     |

актуальной проблемой современной ЭКБ СВЧ. Развитие подходов близкой интеграции идет как в монолитном направлении — монолитная гетерогенная интеграция и монтаж пластина-к-пластине, так и гибридно-монолитном — метод переноса слоев, интеграция в единую подложку, применение аддитивных технологий, перевернутый монтаж и hot-via.

Монолитная гетерогенная интеграция и монтаж пластина-к-пластине не реализуют концепцию ГМИС. Современные технологические ограничения и стоимость получаемого изделия являются ограничивающими факторами развития данных направлений. Метод переноса слоев также требует специальных технологических возможностей, что сдерживает его развитие и применение. Интеграция методом печати обеспечивает промежуточные электрические характеристики и габаритные размеры между методом проволочной интеграции и остальными методами, что делает применение подхода переходным этапом. Необходимость

специфичного дорогостоящего оборудования и технологические ограничения оставляют крайне ограниченную область для применения.

Интеграция в единую подложку из-за разных вариантов реализации позволяет обеспечить уникальные характеристики, например благодаря интеграции магнитных материалов. Данный метод подразумевает применение ряда полупроводниковых технологических этапов, что ведет к повышенной сложности технологических процессов интеграции.

Метод перевернутого монтажа обеспечивает минимальные потери и паразитные составляющие переходных межсоединений в СВЧ-диапазоне благодаря миниатюризации переходных межсоединений. Ноt-via, как модификация метода перевернутого монтажа, обеспечивает лучшую совместимость со схемами с микрополосковыми линиями. Их дальнейшее совершенствование и массовое применение во многом зависят от развития технологии формирования локальных переходных межсоединений.

## Список литературы

1. Connecting Chips with More Than 100 GHz Bandwidth / W. Heinrich, M. Hossain, S. Sinha, F.-J. Schmückle, R. Doerner, V. Krozer, N. Weimann // IEEE J. Microw. 2021. Vol. 1, № 1. P. 364–373. doi: 10.1109/JMW.2020.3032879

2. Heterogeneously Integrated RF Circuits Using Highly Scaled off-the-Shelf GaN HEMT Chiplets / F. Herrault, J. C. Wong, Y. Tang, H. Y. Tai, I. Ramos // IEEE Microwave and Wireless Components Let. 2020. Vol. 30, № 11. P. 1061–1064. doi: 10.1109/LMWC.2020.3025126

- 3. III-V/III-N technologies for next generation high-capacity wireless communication / N. Collaert, A. Alian, A. Banerjee, G. Boccardi P. Cardinael et al. // Intern. Electron Devices Meeting (IEDM). San Francisco, USA, 03–07 Dec. 2022. IEEE, 2022. P. 11.5.1–11.5.4. doi: 10.1109/IEDM45625.2022.10019555

- 4. OMMIC D01PH технологический процесс. URL: https://www.macom.com/european-semiconductor-center/mesc-processes (дата обращения 24.08.2023)

- 5. High Performance and High Reliability of 0.1µm InP HEMT MMIC Technology on 100 mm InP Substrates / R. Lai, Y. C. Chou, L. J. Lee, P. H. Liu, D. Leung, Q. Kan, X. Mei, C. H. Lin, D. Farkas, M. Barsky, D. Eng, A. Cavus, M. Lange, P. Chin, M. Wojtowicz, T. Block, A. Oki // IEEE 19<sup>th</sup> Intern. Conf. on Indium Phosphide & Related Materials, Matsue, Japan, 14–18 May 2007. IEEE, 2007. P. 63–66. doi: 10.1109/ICIPRM.2007.381123

- 6. 6W Ka Band Power Amplifier and 1.2dB NF X-Band Amplifier Using a 100nm GaN/Si Process / R. Leblanc, N. Santos Ibeas, A. Gasmi, F. Auvray, J. Poulain, F. Lecourt, G. Dagher, P. Frijlink // IEEE Compound Semiconductor Integrated Circuit Symp. (CSICS), Austin, TX, USA, 23–26 Oct. 2016. IEEE, 2016. P. 1–4. doi: 10.1109/CSICS.2016.7751009

- 7. 0.13  $\mu$  m SiGe BiCMOS Technology Fully Dedicated to mm-Wave Applications / G. Avenier, M. Diop, P. Chevalier, G. Troillard, N. Loubet et al. // IEEE J. of Solid-State Circuits. 2009. Vol. 44, N 9. P. 2312–2321. doi: 10.1109/JSSC.2009.2024102

- 8. A 0.13-/spl mu/m SOI CMOS technology for low-power digital and RF applications / N. Zamdmer, A. Ray, J.-O. Plouchart, L. Wagner, N. Fong, K. A. Jenkins, W. Jin, P. Smeys, I. Yang, G. Shahidi, F. Assaderghi // Symp. on VLSI Technology. Digest of Technical Papers, Kyoto, Japan, 12–14 June 2001. IEEE, 2001. P. 85–86. doi: 10.1109/VLSIT.2001.934959

- 9. A Novel Si–GaN Monolithic Integration Technology for a High-Voltage Cascoded Diode / J. Ren, C. Liu, C. W. Tang, K. M. Lau, J. K. O. Sin // IEEE Electron Device Let. 2017. Vol. 38, № 4. P. 501–504. doi: 10.1109/LED.2017.2665698

- 10. Pat. US 8823146B1. Semiconductor structure having silicon devices, column III-Nitride devices, and column III-non-Nitride or Column II-VI devices / W. E. Hoke. 02.09. 2014.

- 11. Kazior T. E. Beyond CMOS: heterogeneous integration of III–V devices, RF MEMS and other dissimilar materials/devices with Si CMOS to create intelligent microsystems // Phil. Trans. R. Soc. A. 2014. Vol. 372, № 2012. P. 20130105. doi: 10.1098/rsta.2013.0105

- 12. Silicon-on-insulator with hybrid orientations for heterogeneous integration of GaN on Si (100) substrate / R. Zhang, B. Zhao, K. Huang, T. You, Q. Jia, J. Lin, S. Zhang, Y. Yan, A. Yi, M. Zhou, X. Ou // AIP Advances. 2018. Vol. 8, № 5. P. 055323. doi: 10.1063/1.5030776

- 13. Kazior T. E., LaRoche J. R., Hoke W. E. More Than Moore: GaN HEMTs and Si CMOS Get It To-

- gether // IEEE Compound Semiconductor Integrated Circuit Symp. (CSICS), Monterey, CA, USA, 13–16 Oct. 2013. IEEE, 2013. P. 1–4. doi: 10.1109/CSICS.2013.6659239

- 14. Mendes J. C., Liehr M., Li C. Diamond/GaN HEMTs: Where from and Where to? // Materials. 2022. Vol. 15, № 2. P. 415. doi: 10.3390/ma15020415

- 15. Heteroepitaxial Growth of III-V Semiconductors on Silicon / J.-S. Park, M. Tang, S. Chen, H. Liu // Crystals. 2020. Vol. 10, iss. 12. P. 1163. doi: 10.3390/cryst10121163

- 16. A review of silicon-based wafer bonding processes, an approach to realize the monolithic integration of Si-CMOS and III–V-on-Si wafers / S. Bao, Y. Wang, K. Lina, L. Zhang, B. Wang, W. A. Sasangka, K. E. K. Lee, S. J. Chua, J. Michel, E. Fitzgerald, C. S. Tan, K. H. Lee // J. Semicond. 2021. Vol. 42, № 2. P. 023106. doi: 10.1088/1674-4926/42/2/023106

- 17. InAlN/GaN-on-Si HEMT with 4.5 W/mm in a 200-mm CMOS-Compatible MMIC Process for 3D Integration / S. Warnock, C.-L.Chen, J. Knechtl, R. Molnar et al. // IEEE/MTT-S Intern. Microwave Symp. (IMS). 2020. Los Angeles, CA, USA, 04–06 Aug. 2020. IEEE, 2020. P. 289–292. doi: 10.1109/IMS30576.2020.9224061

- 18. Si/InP Heterogeneous Integration Techniques from the Wafer-Scale (Hybrid Wafer Bonding) to the Discrete Transistor (Micro-Transfer Printing) / A. D. Carter, M. E. Urteaga, Z. M. Griffith, K.-J. Lee, J. Roderick, P. Rowell, J. Bergman, S. Hong, R. Patti, C. Petteway, G. Fountain, K. Ghosel, C. A. Bower // IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conf. (S3S), Burlingame, CA, USA, 15–18 Oct. 2018. IEEE, 2018. P. 1–4. doi: 10.1109/S3S.2018.8640196

- 19. LaRoche J. Towards a Si foundry-compatible GaN-on-Si MMIC process on 200 mm Si with Cu damascene BEOL (Conf. Presentation) // Proc. SPIE 11280, Gallium Nitride Materials and Devices XV, 112801G, 10 March 2020. doi: 10.1117/12.2543913

- 20. A Hetero-Integrated W-Band Transmitter Module in InP-on-BiCMOS Technology / M. Hossain, M. H. Eissa, M. Hrobak, D. Stoppel, N. Weimann, A. Malignaggi, A. Mai, D. Kissinger, W. Heinrich, V. Krozer // 13<sup>th</sup> European Microwave Integrated Circuits Conf. (EuMIC), Madrid, Spain, 23–25 Sept. 2018. IEEE, 2018. P. 97–100. doi: 10.23919/EuMIC.2018.8539915

- 21. Transfer print techniques for heterogeneous integration of photonic components / B. Corbett, R. Loi, W. Zhou, D. Liu, Z. Ma // Progress in Quantum Electronics. 2017. Vol. 52. P. 1–17. doi: 10.1016/j.pquantelec.2017.01.001

- 22. Gong Z. Layer-Scale and Chip-Scale Transfer Techniques for Functional Devices and Systems: A Review // Nanomaterials. 2021. Vol. 11, iss. 4. Art. 842. P. 1–47. doi: 10.3390/nano11040842

- 23. Moutanabbir O., Gösele U. Heterogeneous Integration of Compound Semiconductors // Annual Review of Materials Research. 2010. Vol. 40, iss. 1. P. 469–500. doi: 10.1146/annurev-matsci-070909-104448

- 24. Lerner R., Hansen N. H. Commercial Sweet Spots for GaN and CMOS Integration by Micro-Transfer-Printing // ISPS'21 Proc. Prague, Czech Technical University. 2021. P. 99–106. doi: 10.14311/ISPS.2021.015

- 25. Micro-transfer Printing of GaN HEMTs for Heterogeneous Integration and Flexible RF Circuit Design / B. P. Downey, A. Xie, S. Mack, D. S. Katzer, J. G. Champlain, Yu Cao, N. Nepal, T. A. Growden, V. J. Gokhale, R. L. Coffie, M. T. Hardy, E. Beam, C. Lee, D. J. Meyer // Device Research Conf., Columbus, OH, USA, 21–24 June 2020. IEEE, 2020. P. 1–2. doi: 10.1109/DRC50226.2020.9135179

- 26. A compact and low-profile GaN power amplifier using interposer-based MMIC technology / D. Kim, J. M. Yook, S. J. An, S. R. Kim, J.-G. Yook, J. C. Kim // IEEE 16<sup>th</sup> Electronics Packaging Technology Conf., Singapore, 03–05 Dec. 2014. IEEE, 2014. P. 672–675. doi: 10.1109/EPTC.2014.7028416

- 27. Kompa G., Wasige E., Joodaki M. Quasi Monolithic Hybrid Technology Based on Si Micromachining and Low-Temperature Thin-Film Processing // World Micro-technologies Congress of MICRO-TEC. 2000. Sep. P. 109–114.

- 28. Metal-Embedded Chiplet Assembly for Microwave Integrated Circuits / F. Herrault, J. C. Wong, D. Regan, D. F. Brown, H. Fung, Y. Tang, H. Sharifi // IEEE Transactions on Components, Packaging and Manufacturing Technology. 2020. Vol. 10, № 9. P. 1579–1582. doi: 10.1109/TCPMT.2020.3012505

- 29. Si-Embedded IC Package for W-band Applications: Interconnection Analysis / H.-B. Lee, B.-W. Min, Y.-G. Kim, J. M. Yook, S. Kim, W. Kim // IEEE Asia-Pacific Microwave Conf., Singapore, 10–13 Dec. 2019. IEEE, 2019. P. 1080–1082. doi: 10.1109/APMC46564.2019.9038484

- 30. Metal-Embedded Chip Assembly Processing for Enhanced RF Circuit Performance / A. Estrada, G. Lasser, M. Pinto, F. Herrault, Z. Popović // IEEE Transactions on Microwave Theory and Techniques. 2019. Vol. 67, № 9. P. 3537–3546. doi: 10.1109/TMTT.2019.2931010

- 31. Monolithically Integrated Self-Biased Circulator for mmWave T/R MMIC Applications / Y. Cui, H.-Y. Chen, S. Chen, D. Linkhart, H. Tan et al. // IEEE Intern. Electron Devices Meeting. 2021. P. 4.2.1–4.2.4. doi: 10.1109/IEDM19574.2021.9720611

- 32. Additively Manufactured mm-Wave Multichip Modules with Fully Printed 'Smart' Encapsulation Structures / X. He, B. K. Tehrani, R. Bahr, W. Su, M. M. Tentzeris // IEEE Trans. Microwave Theory Techn. 2020. Vol. 68, № 7. P. 2716–2724. doi: 10.1109/TMTT.2019.2956934

- 33. Additive Manufacturing of a W-Band System-on-Package / M. T. Craton, X. Konstantinou, J. D. Albrecht, P. Chahal, J. Papapolymerou // IEEE Transactions on Microwave Theory and Techniques. 2021. Vol. 69, № 9. P. 4191–4198. doi: 10.1109/TMTT.2021.3076066

- 34. Cung G., Spence T., Borodulin P. Enabling broadband, highly integrated phased array radiating elements through additive manufacturing // IEEE Intern. Symp. on Phased Array Systems and Technology, Waltham, MA, USA, 18–21 Oct. 2016. IEEE, 2016. P. 1–9. doi: 10.1109/ARRAY.2016.7832632

- 35. Kolias N. J., Borkowski M. T. The development of T/R modules for radar applications // IEEE/MTT-S Intern. Microwave Symp. Digest, Montreal, QC, Canada, 17–22 June 2012. IEEE, 2012. P. 1–3. doi: 10.1109/MWSYM.2012.6259727

- 36. A Low-Cost 30-W Class X-Band GaN-on-Si MMIC Power Amplifier with a GaAs MMIC Output Matching Circuit / J. Kamioka, Y. Kawamura, Y. Tarui, K. Nakahara, Y. Kamo, H. Okazaki, M. Hangai, K. Yamanaka, H. Fukumoto // 13<sup>th</sup> European Microwave Integrated Circuits Conf., Madrid, Spain, 23–25 Sep. 2018. IEEE, 2018. P. 93–96. doi: 10.23919/EuMIC.2018.8539903

- 37. Interconnects Analyses in Quasi-Monolithic Integration Technology / M. Joodaki, A. Kricke, H. Hillmer, G. Kompa // IEEE Electrical Performane of Electronic Packaging, Scottsdale, AZ, USA, 23–25 Oct. 2006. IEEE, 2006. P. 229–232. doi: 10.1109/EPEP.2006.321236

- 38. A Cost-Effective Flip-Chip Interconnection for Applications from DC until 200 GHz / P. V. Testa, H. Morath, P. Goran, C. Carta, F. Ellinger // IEEE Asia-Pacific Conf. on Applied Electromagnetics, Melacca, Malaysia, 25–27 Nov. 2019. IEEE, 2019. P. 1–6. doi: 10.1109/APACE47377.2019.9021003

- 39. Design considerations for a new generation of SiPMs with unprecedented timing resolution / S. Enoch, A. Gola, P. Lecoq, A. Rivetti // J. Inst. 2021. Vol. 16, № 02. P. P02019–P02019. doi: 10.1088/1748-0221/16/02/P02019

- 40. Generational changes of flip chip interconnection technology / W. S. Tsai, C. Y. Huang, C. K. Chung, K. H. Yu, C. F. Lin // 12<sup>th</sup> Intern. Microsystems, Packaging, Assembly and Circuits Technology Conf. (IMPACT), Taipei, Taiwan, 25–27 Oct. 2017. IEEE, 2017. P. 306–310. doi: 10.1109/IMPACT.2017.8255955

- 41. Path to 3D heterogeneous integration / D. S. Green, C. L. Dohrman, J. Demmin, T.-H. Chang // Intern. 3D Systems Integration Conf. (3DIC), Sendai, Japan, 31 Aug.–02 Sep. 2015. IEEE, 2015. P. FS7.1–FS7.3. doi: 10.1109/3DIC.2015.7334469

- 42. Wafer-level Au–Au bonding in the 350–450 °C temperature range / H. R Tofteberg, K. Schjølberg-Henriksen, E. J. Fasting, A. S. Moen, M. W. Taklo, E. U. Poppe, C. J. Simensen // J. of Micromechanics and Microengineering. 2014. Vol. 24, iss. 8. P. 084002. doi: 10.1088/0960-1317/24/8/084002

- 43. Recent progress in SLID bonding in novel 3D-IC technologies / L. Sun, M.-H. Chen, L. Zhang, P. He, L.-S. Xie // J. of Alloys and Compounds. 2020. Vol. 818. Art. 152825. doi: 10.1016/j.jallcom.2019.152825

- 44. Technology for the Heterointegration of InP DHBT Chiplets on a SiGe BiCMOS Chip for mm-wave

- MMICs / M. Rausch, T. Flisgen, C. Stolmacker, A. Stranz, A. Thies, R. Doerner, H. Yacoub, W. Heinrich // 52<sup>nd</sup> European Microwave Conf. (EuMC), Milan, Italy, 27–29 Sep. 2022. IEEE, 2022. P. 28–31. doi: 10.23919/EuMC54642.2022.9924451

- 45. Flip-Chip Integration of III-V Chips on Wafer for mmW Applications / A. S. Efimov, A. A. Zaycev, A. S. Kurochka, A. M. Temnov, K. V. Dudinov, A. M. Emelianov, D. D. Korolkova, A. D. Rudina, Y. S. Ranzhin // IEEE 8<sup>th</sup> All-Russ. Microwave Conf. (RMC), Moscow, Russia, 23–25 Nov. 2022. IEEE, 2022. P. 220–222. doi: 10.1109/RMC55984.2022.10079408

- 46. Li C.-H., Hsieh W.-T., Chiu T.-Y. A Flip-Chip-Assembled W-Band Receiver in 90-nm CMOS and IPD Technologies // IEEE Transactions on Microwave Theory and Techniques. 2019. Vol. 67, № 4. P. 1628–1639. doi: 10.1109/TMTT.2019.2894426

- 47. Encapsulated Organic Package Technology for Wideband Integration of Heterogeneous MMICs / S. Pavlidis, G. Alexopoulos, A. Ç. Ulusoy, M. Cho, J. Papapolymerou // IEEE Transactions on Microwave Theory and Techniques. 2017. Vol. 65, № 2. P. 438–448. doi: 10.1109/TMTT.2016.2630067

- 48. Heinrich W. The flip-chip approach for millimeter wave packaging // IEEE Microwave Magazine. 2005. Vol. 6, № 3. P. 36–45. doi: 10.1109/MMW.2005.1511912

- 49. Fan-out Wafer Level Packaging of GaN Traveling Wafer Amplifier / D. Schwantuschke, E. Ture, T. Braun, T. D. Nguyen, M. Wohrmann, M. Pretl, S. Engels // IEEE/MTT-S Intern. Microwave Symp. IMS 2022, Denver, CO, USA, 19–24 June 2022. IEEE, 2022. P. 579–582. doi: 10.1109/IMS37962.2022.9865579

- 50. Feghhi R., Joodaki M. Thermal analysis of microwave GaN-HEMTs in conventional and flip-chip

- assemblies // Intern. J. of RF and Microwave Computer-Aided Engineering. 2018. Vol. 28, iss. 8. Art. e21513. doi: 10.1002/mmce.21513

- 51. A Millimeter-Wave System-on-Package Technology Using a Thin-Film Substrate With a Flip-Chip Interconnection / S. Song, Y. Kim, J. Maeng, H. Lee, Y. Kwon, K.-S. Seo // IEEE Transactions on Advanced Packaging. 2009. Vol. 32, no. 1. P. 101–108. doi: 10.1109/TADVP.2008.2006626

- 52. Transceiver MMIC's for street surveillance radar / K. Tsukashima, O. Anegawa, T. Kawasaki, A. Otsuka, M. Kubota, T. Tokumitsu, S. Ogita // 11<sup>th</sup> European Microwave Integrated Circuits Conf. (EuMIC), London, UK, 03–04 Oct. 2016. IEEE, 2016. P. 329–332. doi: 10.1109/EuMIC.2016.7777557

- 53. DBIT-direct backside interconnect technology: a manufacturable, bond wire free interconnect technology for microwave and millimeter wave MMICs / T. E. Kazior, H. N. Atkins, A. Fatemi, Y. Chen, F. Y. Colomb, J. P. Wendler // IEEE MTT-S Intern. Microwave Symp., Digest. Denver, CO, USA, 08–13 June 1997. IEEE, 1997. P. 723–726. doi: 10.1109/MWSYM.1997.602892

- 54. A Hot-via Chip-to-substrate Interconnect for Ultra-compact System Package Application up to W Band / J. Yang, B. Zou, J. Xu, J. Zhou // PIER Let. 2022. Vol. 107. P. 75–81. doi: 10.2528/PIERL22020201

- 55. Millimetre-wave Hot-Via interconnect-based GaAs chip-set for automotive RADAR and security sensors / PF. Alleaume, C. Toussain, C. Auvinet, D. Domnesque, P. Quentin, M. Camiade // European Microwave Integrated Circuit Conf., Amsterdam, Netherlands, 27–28 Oct. 2008. IEEE, 2008. P. 52–55. doi: 10.1109/EMICC.2008.4772226

## Информация об авторе

**Ефимов Александр Сергеевич** – магистр по направлению "Электроника и наноэлектроника" (Рязанский государственный радиотехнический университет, 2017), инженер 2-й категории АО «НПП "Исток" им. Шокина». Автор более 15 научных работ. Сфера научных интересов – широкозонные полупроводники; усилители мощности и малошумящие усилители СВЧ; интеграция микроэлектроники СВЧ.

Адрес: АО «НПП "Исток" им. Шокина», ул. Вокзальная, д. 2а, Фрязино, 141190, Россия

E-mail: easmov@gmail.com

https://orcid.org/0000-0002-6792-1096

## References

- 1. Heinrich W., Hossain M., Sinha S., Schmückle F.-J., Doerner R., Krozer V., Weimann N. Connecting Chips with More Than 100 GHz Bandwidth. IEEE J. Microw. 2021, vol. 1, no. 1, pp. 364–373. doi: 10.1109/JMW.2020.3032879

- 2. Herrault F., Wong J. C., Tang Y., Tai H. Y., Ramos I. Heterogeneously Integrated RF Circuits Using Highly Scaled off-the-Shelf GaN HEMT Chiplets. IEEE Microwave and Wireless Components Let. 2020, vol. 30, no. 11, pp. 1061–1064. doi: 10.1109/LMWC.2020.3025126

- 3. Collaert N., Alian A., Banerjee A., Boccardi G., Cardinael P. et al. III-V/III-N Technologies for Next

- Generation High-Capacity Wireless Communication. 2022 Intern. Electron Devices Meeting (IEDM), San Francisco, USA, 03–07 Dec. 2022. IEEE, 2022, pp. 11.5.1–11.5.4. doi: 10.1109/IEDM45625.2022. 10019555

- 4. OMMIC D01PH Technological Process. Available at: https://www.macom.com/european-semiconductor-center/mesc-processes (accessed 24.08.2023)

- 5. Lai R., Chou Y. C., Lee L. J., Liu P. H., Leung D., Kan Q., Mei X., Lin C. H., Farkas D., Barsky M., Eng D., Cavus A., Lange M., Chin P., Wojtowicz M., Block T., Oki A. High Performance and High Reliability of 0.1μm InP HEMT MMIC Technol-

- ogy on 100 mm InP Substrates. IEEE 19<sup>th</sup> Intern. Conf. on Indium Phosphide & Related Materials, Matsue, Japan, 14–18 May 2007. IEEE, 2007, pp. 63–66. doi: 10.1109/ICIPRM.2007.381123

- 6. Leblanc R., Santos Ibeas N., Gasmi A., Auvray F., Poulain J., Lecourt F., Dagher G., Frijlink P. 6W Ka Band Power Amplifier and 1.2dB NF X-Band Amplifier Using a 100nm GaN/Si Process. 2016 IEEE Compound Semiconductor Integrated Circuit Symp. (CSICS), Austin, TX, USA, 23–26 Oct. 2016. IEEE, 2016, pp. 1–4. doi: 10.1109/CSICS.2016.7751009

- 7. Avenier G., Diop M., Chevalier P., Troillard G., Loubet N. et al. 0.13  $\mu$  m SiGe BiCMOS Technology Fully Dedicated to mm-Wave Applications. IEEE J. of Solid-State Circuits. 2009, vol. 44, no. 9, pp. 2312–2321. doi: 10.1109/JSSC.2009.2024102